Microprocesadores P1020NXN2HFB: MPU 800/400/667 ET NE r1.1

♠ Descrición do produto

| Atributo do produto | Valor do atributo |

| Fabricante: | NXP |

| Categoría do produto: | Microprocesadores - MPU |

| Directiva RoHS: | Detalles |

| Estilo de montaxe: | SMD/SMT |

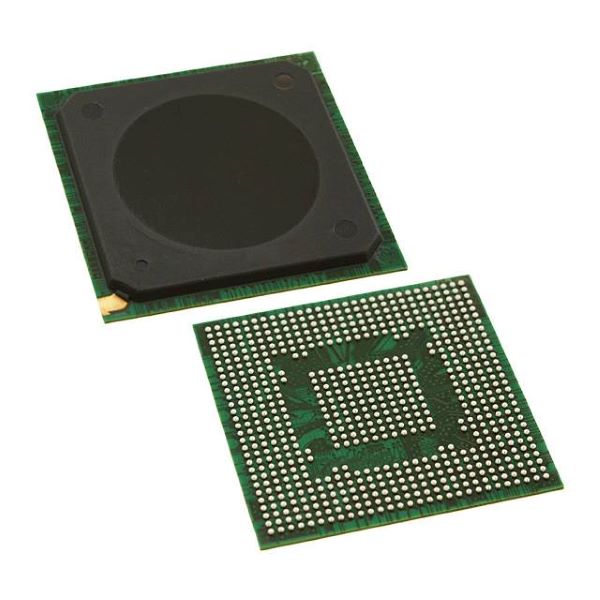

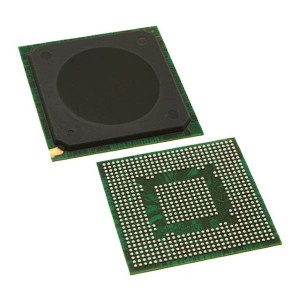

| Paquete/Caixa: | TEPBGA-689 |

| Serie: | P1020 |

| Núcleo: | e500 |

| Número de núcleos: | 2 núcleos |

| Largura do bus de datos: | 32 bits |

| Frecuencia máxima de reloxo: | 800 MHz |

| Memoria de instrucións da caché L1: | 2 x 32 kB |

| Memoria de datos da caché L1: | 2 x 32 kB |

| Tensión de alimentación de funcionamento: | 1 V |

| Temperatura mínima de funcionamento: | - 40 °C |

| Temperatura máxima de funcionamento: | + 125 °C |

| Embalaxe: | Bandexa |

| Marca: | Semicondutores NXP |

| Voltaxe de E/S: | 1,5 V, 1,8 V, 2,5 V, 3,3 V |

| Tipo de instrución: | Coma flotante |

| Tipo de interface: | Ethernet, I2C, PCIe, SPI, UART, USB |

| Instrucións de caché L2 / Memoria de datos: | 256 kB |

| Tipo de memoria: | Caché L1/L2 |

| Sensible á humidade: | Si |

| Número de E/S: | 16 E/S |

| Serie de procesadores: | QorIQ |

| Tipo de produto: | Microprocesadores - MPU |

| Cantidade do paquete de fábrica: | 27 |

| Subcategoría: | Microprocesadores - MPU |

| Nome comercial: | QorIQ |

| Temporizadores de vixilancia: | Sen temporizador de vixilancia |

| Alias de número de peza: | 935310441557 |

| Peso unitario: | 5,247 gramos |

• Núcleos duplos de alto rendemento de 32 bits, baseados na tecnoloxía Power Architecture®:

– Enderezo físico de 36 bits

– Soporte de coma flotante de dobre precisión

– 32 Kbyte de caché de instrucións L1 e 32 Kbyte de caché de datos L1 para cada núcleo

– Frecuencia de reloxo de 533 MHz a 800 MHz

• Caché L2 de 256 Kbytes con ECC. Tamén configurable como memoria SRAM e de almacenamento.

• Tres controladores Ethernet de tres velocidades melloradas de 10/100/1000 Mbps (eTSEC)

– Aceleración TCP/IP, calidade de servizo e capacidades de clasificación

– Compatibilidade con IEEE® 1588

– Control de fluxo sen perdas

– MII, RMII, RGMII, SGMII

• Interfaces de alta velocidade que admiten varias opcións de multiplexación:

– Catro SerDes de ata 2,5 GHz/carril multiplexados entre controladores

– Dúas interfaces PCI Express

– Dúas interfaces SGMII

• Controlador USB de alta velocidade (USB 2.0)

– Soporte de host e dispositivo

– Interface de controlador de host mellorada (EHCI)

– Interface ULPI para PHY

• Controlador dixital de host seguro mellorado (SD/MMC)

• Interface periférica serie mellorada (eSPI)

• Motor de seguridade integrado

– A compatibilidade cos protocolos inclúe ARC4, 3DES, AES, RSA/ECC, RNG e SSL/TLS de paso único

– Aceleración XOR

• Controladora de memoria SDRAM DDR2/DDR3 de 32 bits con compatibilidade con ECC

• Controlador de interrupcións programable (PIC) compatible co estándar OpenPIC

• Un controlador DMA de catro canles

• Dous controladores I2C, DUART, temporizadores

• Controlador de bus local mellorado (eLBC)

• TDM

• 16 sinais de E/S de propósito xeral

• Rango de temperatura de funcionamento da unión (Tj): 0–125 °C e de –40 °C a 125 °C (especificación industrial)

• WB-TePBGA II de 31 × 31 mm e 689 pines (BGA de plástico con mellora da temperatura de unión por fíos)