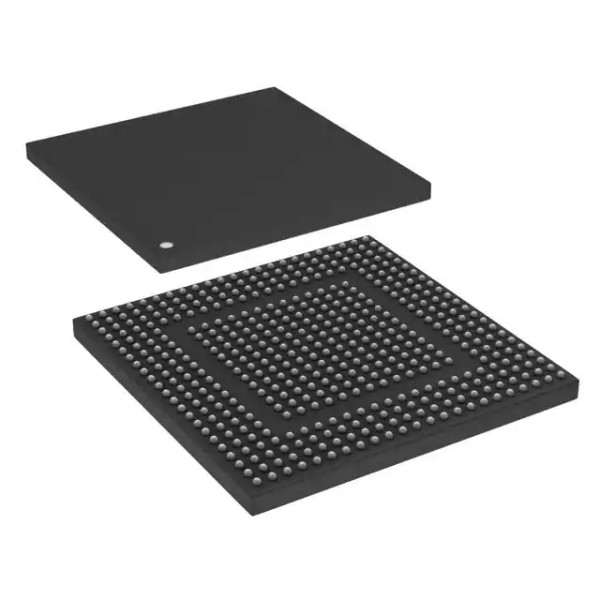

Microcontroladores SPC5675KFF0MMS2 de 32 bits, MCU, 2 M Flash, 512 KSRAM, EBI

♠ Descrición do produto

| Atributo do produto | Valor do atributo |

| Fabricante: | NXP |

| Categoría do produto: | Microcontroladores de 32 bits - MCU |

| Directiva RoHS: | Detalles |

| Serie: | MPC5675K |

| Estilo de montaxe: | SMD/SMT |

| Paquete/Caixa: | BGA-473 |

| Núcleo: | e200z7d |

| Tamaño da memoria do programa: | 2 MB |

| Tamaño da RAM de datos: | 512 kB |

| Largura do bus de datos: | 32 bits |

| Resolución ADC: | 12 bits |

| Frecuencia máxima de reloxo: | 180 MHz |

| Tensión de alimentación - Mín.: | 1,8 V |

| Tensión de alimentación - Máx.: | 3,3 V |

| Temperatura mínima de funcionamento: | - 40 °C |

| Temperatura máxima de funcionamento: | + 125 °C |

| Cualificación: | AEC-Q100 |

| Embalaxe: | Bandexa |

| Tensión de alimentación analóxica: | 3,3 V/5 V |

| Marca: | Semicondutores NXP |

| Tipo de RAM de datos: | SRAM |

| Voltaxe de E/S: | 3,3 V |

| Sensible á humidade: | Si |

| Serie de procesadores: | MPC567xK |

| Produto: | MCU |

| Tipo de produto: | Microcontroladores de 32 bits - MCU |

| Tipo de memoria de programa: | Flash |

| Cantidade do paquete de fábrica: | 420 |

| Subcategoría: | Microcontroladores - MCU |

| Temporizadores de vixilancia: | Temporizador de vixilancia |

| Alias de número de peza: | 935310927557 |

| Peso unitario: | 0,057260 onzas |

♠ Microcontrolador MPC5675K

O microcontrolador MPC5675K, unha solución SafeAssure, é unControlador integrado de 32 bits deseñado para controladores avanzadossistemas de asistencia con RADAR, imaxes CMOS, LIDARe sensores ultrasónicos e control de motores trifásicos múltiplesaplicacións como en vehículos híbridos eléctricos (HEV) enaplicacións automotrices e industriais de alta temperatura.

Un membro da familia MPC5500/5600 de NXP Semiconductor,Contén a arquitectura de enerxía compatible co Libro Enúcleo tecnolóxico con codificación de lonxitude variable (VLE). Istoo núcleo cumpre coa arquitectura Power Architect integradacategoría e é 100% compatible co modo de usuarioarquitectura orixinal do conxunto de instrucións de usuario (UISA) de Power PC™.Ofrece un rendemento do sistema ata catro veces superior ao do seuO seu predecesor, o MPC5561, ao tempo que che ofrece a fiabilidade efamiliaridade coa tecnoloxía probada de Power Architecture.

Un conxunto completo de hardware e softwareferramentas de desenvolvemento dispoñibles para axudar a simplificar e acelerardeseño do sistema. Hai soporte para o desenvolvemento dispoñible a través deprovedores líderes de ferramentas que fornecen compiladores, depuradores eentornos de desenvolvemento de simulación.

• Procesador e200z7d de dobre núcleo de alto rendemento

— CPU con tecnoloxía Power Architecture de 32 bits

— Frecuencia central de ata 180 MHz

— Núcleo de dobre cuestión

— Codificación de lonxitude variable (VLE)

— Unidade de xestión de memoria (MMU) con 64 entradas

— 16 KB de caché de instrucións e 16 KB de caché de datos

• Memoria dispoñible

— Ata 2 MB de memoria flash de código con ECC

— Memoria flash de datos de 64 KB con ECC

— Ata 512 KB de SRAM integrada no chip con ECC

• Concepto de seguridade innovador SIL3/ASILD: modo LockStep e protección a proba de fallos

— Esfera de replicación (SoR) para compoñentes clave

— Unidades de comprobación de redundancia nas saídas do SoR conectadas á FCCU

— Unidade de recollida e control de avarías (FCCU)

— Autocomproba integrada no momento do arranque para a memoria (MBIST) e a lóxica (LBIST) activada polo hardware

— Autocomproba integrada no momento do arranque para ADC e memoria flash

— Temporizador de vixilancia mellorado con seguridade replicado

— Sensor de temperatura do substrato (moeda) de silicio

— Interrupción non enmascarable (NMI)

— Unidade de protección de memoria (MPU) de 16 rexións

— Unidades de monitorización de reloxos (CMU)

— Unidade de xestión de enerxía (PMU)

— Unidades de comprobación de redundancia cíclica (CRC)

• Modo paralelo desacoplado para o uso de alto rendemento de núcleos replicados

• Interface Nexus Clase 3+

• Interrupcións

— Controlador de interrupcións de 16 prioridades replicado

• GPIO programables individualmente como entrada, saída ou función especial

• 3 unidades eTimer de uso xeral (6 canles cada unha)

• 3 unidades FlexPWM con catro canles de 16 bits por módulo

• Interfaces de comunicación

— 4 módulos LINFlex

— 3 módulos DSPI con xeración automática de selección de chips

— 4 interfaces FlexCAN (2.0B Activas) con 32 obxectos de mensaxe

— Módulo FlexRay (V2.1) con dobre canle, ata 128 obxectos de mensaxe e ata 10 Mbit/s

— Controlador Ethernet rápido (FEC)

— 3 I2Módulos C

• Catro conversores analóxico-dixitais (ADC) de 12 bits

— 22 canles de entrada

— Unidade de disparo cruzado programable (CTU) para sincronizar a conversión ADC co temporizador e PWM

• Interface de bus externo

• Controladora de memoria DDR externa de 16 bits

• Interface dixital paralela (PDI)

• Cargador de arranque CAN/UART integrado no chip

• Capaz de funcionar cunha única fonte de alimentación de 3,3 V

— Módulos só de 3,3 V: E/S, osciladores, memoria flash

— Módulos de 3,3 V ou 5 V: ADC, alimentación a VREG interno

— Rango de alimentación de 1,8 a 3,3 V: DRAM/PDI

• Rango de temperatura de funcionamento da unión: de –40 a 150 °C