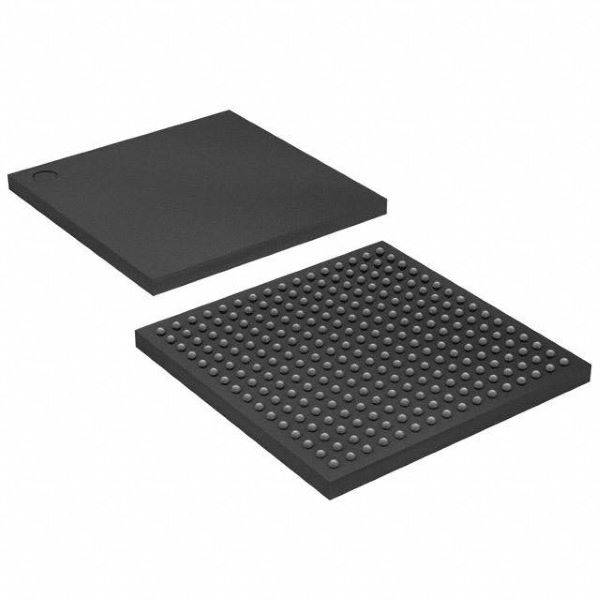

XC6SLX25-2FTG256C FPGA: Matriz de portas programables en campo. A fábrica non acepta pedidos para este produto actualmente.

♠ Descrición do produto

| Atributo do produto | Valor do atributo |

| Fabricante: | Xilinx |

| Categoría do produto: | FPGA - Matriz de portas programables en campo |

| Directiva RoHS: | Detalles |

| Serie: | XC6SLX25 |

| Número de elementos lóxicos: | 24051 LE |

| Número de E/S: | 186 E/S |

| Tensión de alimentación - Mín.: | 1,14 V |

| Tensión de alimentación - Máx.: | 1,26 V |

| Temperatura mínima de funcionamento: | 0 °C |

| Temperatura máxima de funcionamento: | + 85 °C |

| Velocidade de datos: | - |

| Número de transceptores: | - |

| Estilo de montaxe: | SMD/SMT |

| Paquete/Caixa: | FBGA-256 |

| Marca: | Xilinx |

| RAM distribuída: | 229 kbits |

| Memoria RAM de bloque integrada - EBR: | 936 kbits |

| Frecuencia máxima de funcionamento: | 1080 MHz |

| Sensible á humidade: | Si |

| Número de bloques de matriz lóxica - LABs: | LABORATORIO DE 1879 |

| Tensión de alimentación de funcionamento: | 1,2 V |

| Tipo de produto: | FPGA - Matriz de portas programables en campo |

| Cantidade do paquete de fábrica: | 1 |

| Subcategoría: | Circuitos integrados de lóxica programable |

| Nome comercial: | Espartano |

| Peso unitario: | 21,576 gramos |

♠ Visión xeral da familia Spartan-6

A familia Spartan®-6 ofrece capacidades de integración de sistemas líderes co menor custo total para aplicacións de alto volume. A familia de trece membros ofrece densidades ampliadas que van dende 3840 ata 147443 celas lóxicas, coa metade do consumo de enerxía das familias Spartan anteriores e unha conectividade máis rápida e completa. Construída sobre unha tecnoloxía de proceso de cobre de baixo consumo de 45 nm madura que ofrece o equilibrio óptimo entre custo, potencia e rendemento, a familia Spartan-6 ofrece unha nova lóxica de táboa de consulta (LUT) de 6 entradas e dobre rexistro máis eficiente e unha rica selección de bloques de nivel de sistema integrados. Estes inclúen RAM de bloque de 18 Kb (2 x 9 Kb), porcións DSP48A1 de segunda xeración, controladores de memoria SDRAM, bloques de xestión de reloxo de modo mixto mellorados, tecnoloxía SelectIO™, bloques de transceptor serie de alta velocidade con optimización de enerxía, bloques de punto final compatibles con PCI Express®, modos avanzados de xestión de enerxía a nivel de sistema, opcións de configuración de detección automática e seguridade IP mellorada con protección AES e Device DNA. Estas características proporcionan unha alternativa programable de baixo custo aos produtos ASIC personalizados cunha facilidade de uso sen precedentes. As FPGA Spartan-6 ofrecen a mellor solución para deseños lóxicos de alto volume, deseños DSP orientados ao consumidor e aplicacións integradas sensibles ao custo. As FPGA Spartan-6 son a base de silicio programable para plataformas de deseño dirixido que ofrecen compoñentes de software e hardware integrados que permiten aos deseñadores centrarse na innovación en canto comeza o seu ciclo de desenvolvemento.

• Familia Spartan-6:

• Spartan-6 LX FPGA: Optimización lóxica

• Spartan-6 LXT FPGA: Conectividade serie de alta velocidade

• Deseñado para un baixo custo

• Múltiples bloques integrados eficientes

• Selección optimizada de estándares de E/S

• Almofadas escalonadas

• Envases de plástico de gran volume unidos por arame

• Baixa potencia estática e dinámica

• Proceso de 45 nm optimizado para custo e baixo consumo de enerxía

• Modo de hibernación para apagar sen enerxía

• O modo de suspensión mantén o estado e a configuración con activación multipin e mellora do control

• Tensión do núcleo de menor potencia de 1,0 V (só FPGA LX, -1L)

• Tensión de núcleo de alto rendemento de 1,2 V (FPGA LX e LXT, graos de velocidade de -2, -3 e -3N)

• Bancos de interfaces SelectIO™ multitensión e multiestándar

• Ata unha velocidade de transferencia de datos de 1080 Mb/s por E/S diferencial

• Unidade de saída seleccionable, ata 24 mA por pin

• Estándares e protocolos de 3,3 V a 1,2 VI/O

• Interfaces de memoria HSTL e SSTL de baixo custo

• Conformidade coa intercambiabilidade en quente

• Velocidades de variación de E/S axustables para mellorar a integridade do sinal

• Transceptores serie GTP de alta velocidade nas FPGA LXT

• Ata 3,2 Gb/s

• Interfaces de alta velocidade, incluíndo: Serial ATA, Aurora, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort e XAUI

• Bloque de punto final integrado para deseños PCI Express (LXT)

• Compatibilidade coa tecnoloxía PCI® de baixo custo coa especificación de 33 MHz, 32 e 64 bits.

• Seccións DSP48A1 eficientes

• Aritmética e procesamento de sinais de alto rendemento

• Multiplicador rápido de 18 x 18 e acumulador de 48 bits

• Capacidade de canalización e en cascada

• Preagregado para axudar na aplicación do filtro

• Bloques de controlador de memoria integrados

• Compatibilidade con DDR, DDR2, DDR3 e LPDDR

• Velocidades de datos de ata 800 Mb/s (12,8 Gb/s de ancho de banda máximo)

• Estrutura de bus multiporto con FIFO independente para reducir os problemas de tempo de deseño

• Abundantes recursos lóxicos con maior capacidade lóxica

• Compatibilidade opcional con rexistro de desprazamento ou RAM distribuída

• As LUT eficientes de 6 entradas melloran o rendemento e minimizan a enerxía

• LUT con dobres flip-flops para aplicacións centradas en canalizacións

• RAM de bloques cunha ampla gama de granularidade

• RAM de bloques rápida con activación de escritura en bytes

• Bloques de 18 Kb que se poden programar opcionalmente como dúas RAM de bloques independentes de 9 Kb

• Mosaico de xestión de reloxo (CMT) para un rendemento mellorado

• Baixo nivel de ruído e reloxo flexible

• Os xestores de reloxo dixital (DCM) eliminan a asimetría do reloxo e a distorsión do ciclo de traballo

• Bucles de enganche de fase (PLL) para unha sincronización de baixa fluctuación

• Síntese de frecuencia con multiplicación, división e cambio de fase simultáneos

• Dezaseis redes de reloxo globais de baixa asimetría

• Configuración simplificada, compatible con estándares de baixo custo

• Configuración de detección automática de 2 pines

• Amplo soporte para SPI de terceiros (ata x4) e memoria flash NOR

• Plataforma flash Xilinx con moitas funcionalidades e JTAG

• Compatibilidade con MultiBoot para actualización remota con múltiples fluxos de bits, mediante protección watchdog

• Seguridade mellorada para a protección do deseño

• Identificador único de ADN do dispositivo para a autenticación do deseño

• Cifrado de fluxo de bits AES nos dispositivos máis grandes

• Procesamento integrado máis rápido cun procesador MicroBlaze™ mellorado e de baixo custo

• Deseños de referencia e propiedade intelectual líderes na industria